Color online) Schematic energy band diagram of fully programed charge... | Download Scientific Diagram

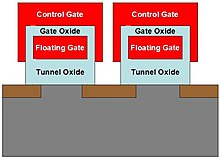

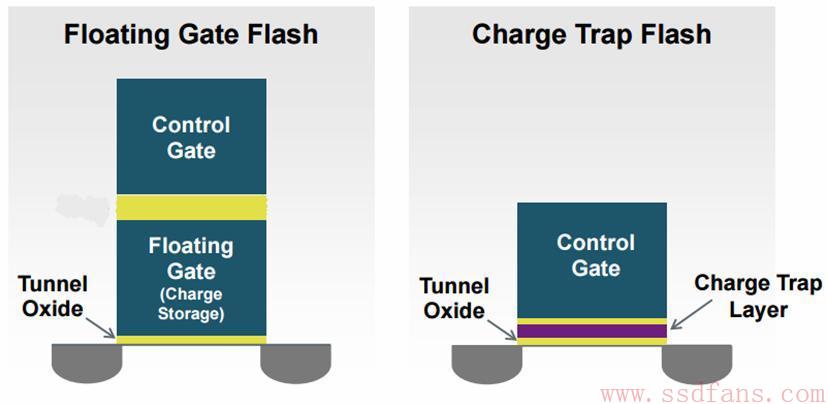

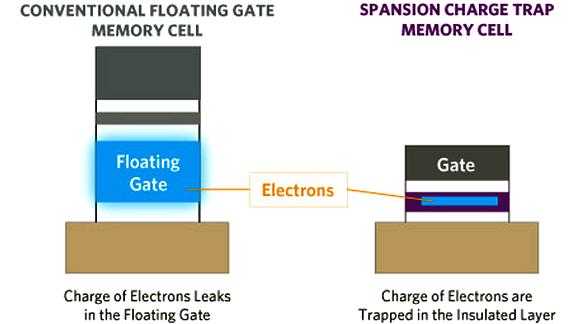

a) A floating gate NAND Flash memory cell which stores charge in the... | Download Scientific Diagram

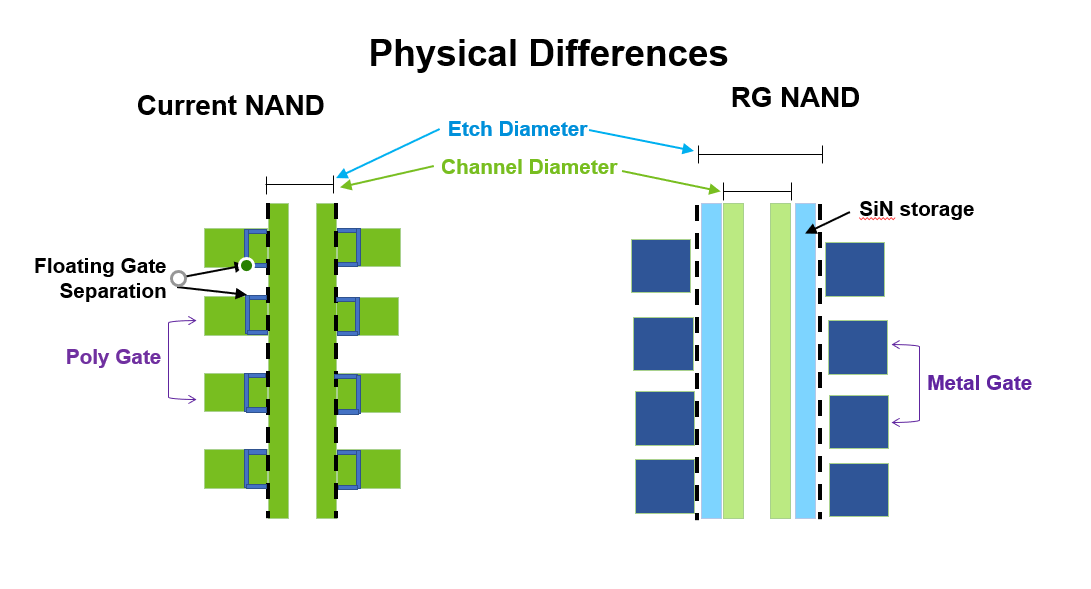

Characterization Summary of Performance, Reliability, and Threshold Voltage Distribution of 3D Charge-Trap NAND Flash Memory | ACM Transactions on Storage

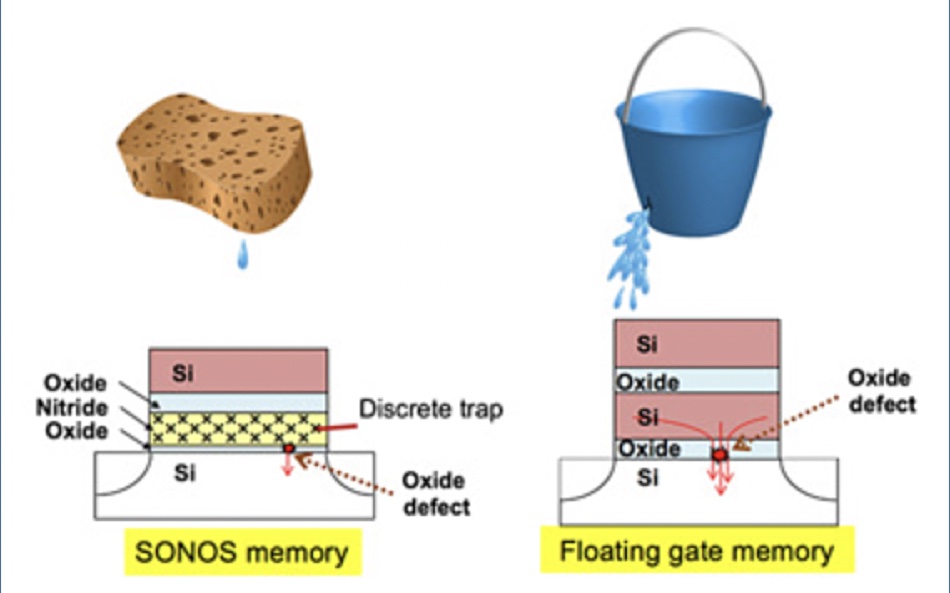

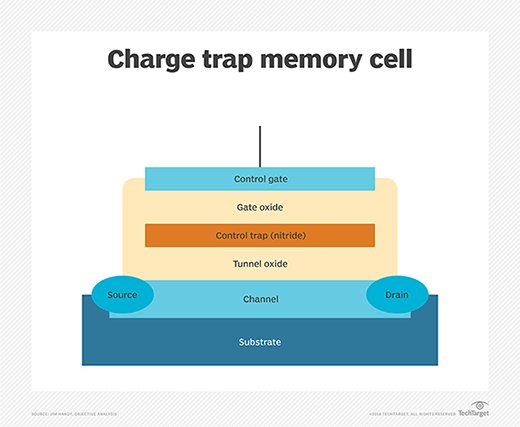

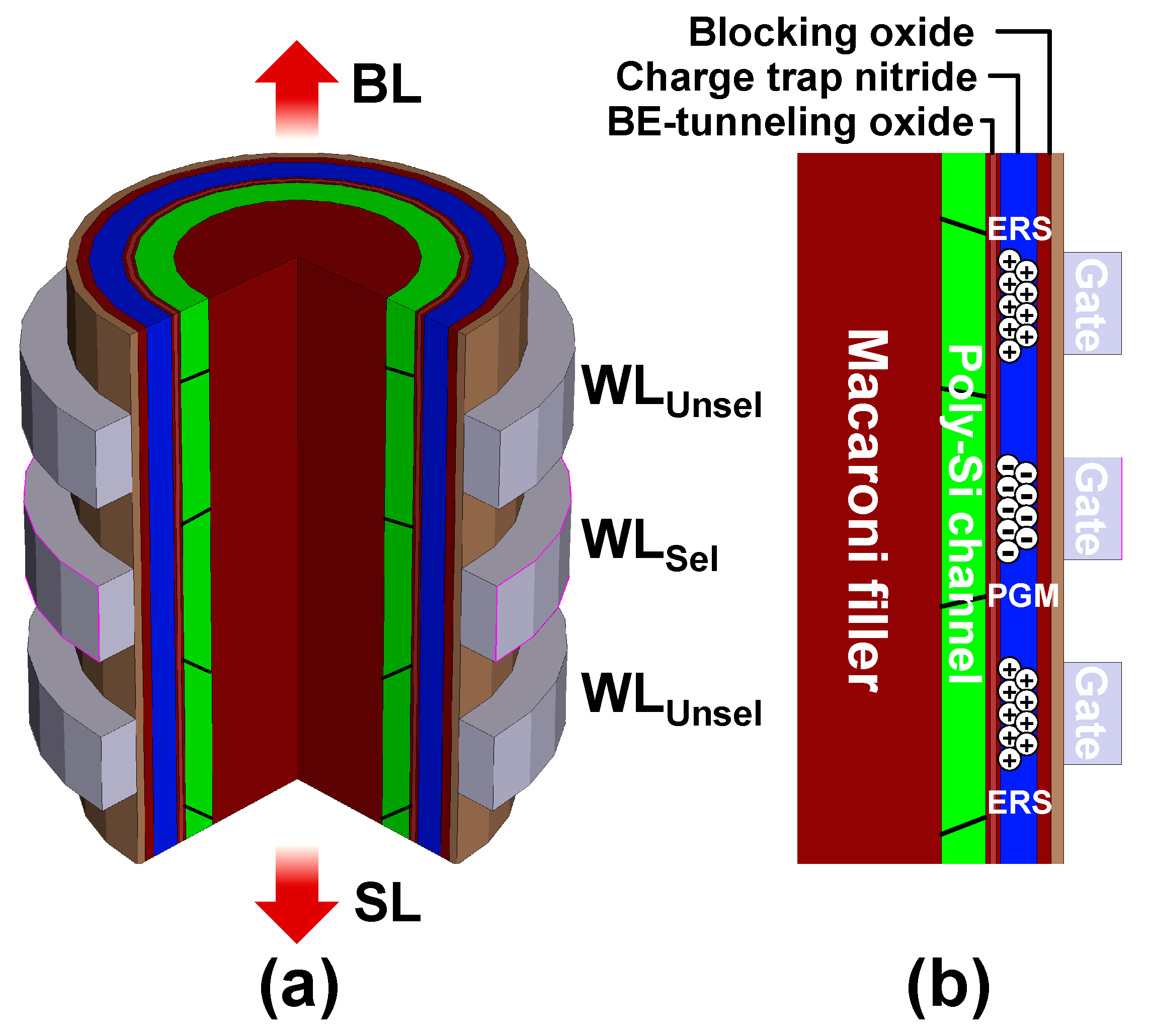

Nanomaterials | Free Full-Text | Optimal Energetic-Trap Distribution of Nano-Scaled Charge Trap Nitride for Wider Vth Window in 3D NAND Flash Using a Machine-Learning Method

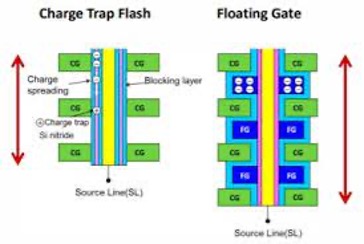

Program/Erase Cycling Enhanced Lateral Charge Diffusion in Triple-Level Cell Charge-Trapping 3D NAND Flash Memory | Semantic Scholar

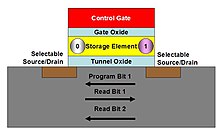

Figure 1 from Dual-Gate Charge Trap Flash Memory for Highly Reliable Triple Level Cell Using Capacitive Coupling Effects | Semantic Scholar

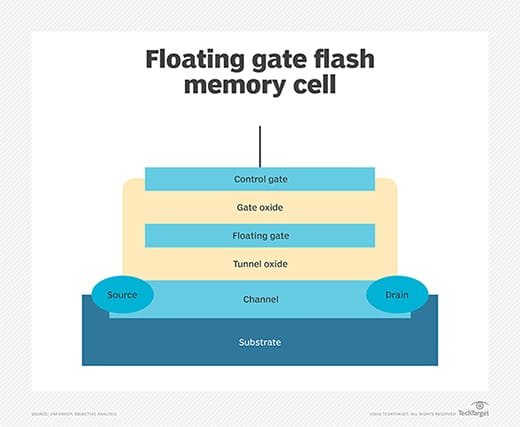

![2001.07424] Investigation of Data Deletion Vulnerabilities in NAND Flash Memory Based Storage 2001.07424] Investigation of Data Deletion Vulnerabilities in NAND Flash Memory Based Storage](https://ar5iv.labs.arxiv.org/html/2001.07424/assets/fg2.png)